## **BRAINWARE UNIVERSITY**

## **Term End Examination 2020 - 21**

Programme – Bachelor of Technology in Computer Science & Engineering

**Course Name – Digital Electronics**

Course Code - BCSE301 Semester / Year - Semester III

| Time | allotte | d • | 85 N    | <b>Minutes</b> |

|------|---------|-----|---------|----------------|

|      | anonc   | и.  | (), ) ! | vimuuos        |

Full Marks: 70

[The figure in the margin indicates full marks. Candidates are required to give their answers in their own words as far as practicable.]

|         | answers in their own wor                     | ds as far as practicable.] |           |

|---------|----------------------------------------------|----------------------------|-----------|

|         | Grou                                         | ıp-A                       |           |

|         | (Multiple Cho                                | ice Type Question)         | 1 x 70=70 |

| 1.      | (Answer any Seventy)                         |                            |           |

| (i) Ka  | rnaugh map is used:                          |                            |           |

| a)      | To draw the digital circuit layout           | b) To simplify logical     | function  |

|         | To locate different gates in a digital reuit | d) None of these           |           |

| (ii) H  | ow many AND gates are required for a         | 8-to-1 multiplexer?        |           |

| a)      | 5                                            | b) 7                       |           |

| c)      | 8                                            | d) 6                       |           |

| (iii) T | Γhe number 140 in octal is equivalent to     | o?                         |           |

| a)      |                                              | b)                         |           |

| (9      | 0) <sub>10</sub>                             | $(88)_{10}$                |           |

| c)      |                                              | d)                         |           |

| (8      | 6) <sub>10</sub>                             | (96) <sub>10</sub>         |           |

| (iv) Ir | n witch of the following base systems is     | s 123 not a valid number?  |           |

| a)      | Base16                                       | b) Base3                   |           |

| c)      | Base10                                       | d) Base8                   |           |

|         |                                              |                            |           |

| (v) The expression Y=AB+BC+AC shows the                                                         | operation.                         |

|-------------------------------------------------------------------------------------------------|------------------------------------|

| a) SOP                                                                                          | b) NOR                             |

| c) POS                                                                                          | d) EX-OR                           |

| (vi) Full subtractor is used to perform subtraction                                             | on of                              |

| a) 4 bits                                                                                       | b) 3 bits                          |

| c) 2 bits                                                                                       | d) 8 bits                          |

| (vii)                                                                                           |                                    |

| The value of base x is: $(211)_x = (152)_8$                                                     |                                    |

| a) 7                                                                                            | b) 8                               |

| c) 6                                                                                            | d) 5                               |

| (viii) Before an SOP implementation, the expr<br>require a total of how many gates?             | ession X= AB(C'D+EF) would         |

| a) 1                                                                                            | b) 2                               |

| c) 4                                                                                            | d) 5                               |

| (ix) Which is the prohibited state/ condition in avoided due to unpredictable nature of output? |                                    |

| a) $S = R = 0$                                                                                  | b) $S = 0$ , $R = 1$               |

| c) $S = 1$ , $R = 0$                                                                            | d) S = R = 1                       |

| (x) Which type of triggering is shown by the D the temporary storage of digital words?          | flip flops in buffer registers for |

| a) Positive level triggering                                                                    | b) Negative level triggering       |

| c) Positive edge triggering                                                                     | d) Negative edge triggering        |

| (xi)                                                                                            |                                    |

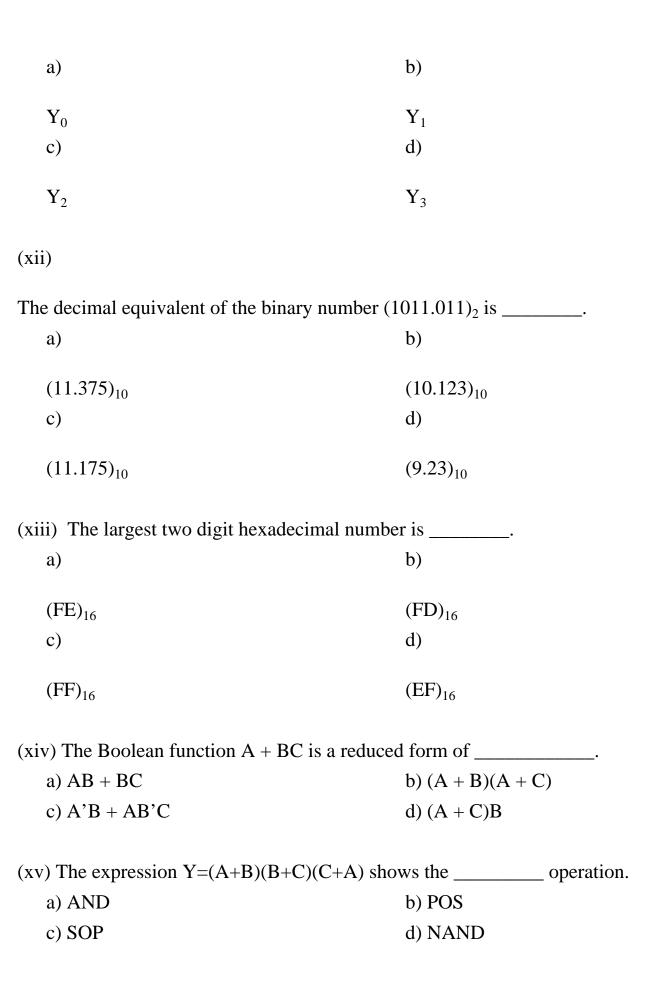

| In 1:4 demultiplexer, if $S_0 = 1 & S_1 = 1$ , then the                                         | ne output will be                  |

| (xvi) Exclusive-OR (XOR) logic gates can be                                                  | e constructed from what other             |

|----------------------------------------------------------------------------------------------|-------------------------------------------|

| logic gates?                                                                                 | h) AND gates and NOT gates                |

| a) OR gates only                                                                             | b) AND gates and NOT gates                |

| c) AND gates, OR gates, and NOT gates                                                        | d) OR gates and NOT gates                 |

| (xvii) In a combinational circuit, the output at at that time.                               | t any time depends only on the            |

| a) Voltage                                                                                   | b) Intermediate values                    |

| c) Input values                                                                              | d) Clock pulses                           |

| (xviii) In a sequential circuit, the output at an values at that time.                       | y time depends only on the input          |

| a) Past output values                                                                        | b) Past output and Present input          |

| c) Intermediate values                                                                       | d) Present input values                   |

| (xix) In parts of the processor, adders are use                                              | d to calculate                            |

| a) Addresse                                                                                  | b) Table indices                          |

| c) Increment and decrement operators                                                         | d) All of these                           |

| (xx) TTL is called transistor–transistor logic function and the amplifying function are perf |                                           |

| a) Resistors                                                                                 | b) Bipolar junction transistors           |

| c) One transistor                                                                            | d) Resistors and transistors respectively |

| (xxi) How many stages a DTL consist of?                                                      |                                           |

| a) 2                                                                                         | b) 3                                      |

| c) 4                                                                                         | d) 5                                      |

| (xxii) How many NOT gates are required to i $X = AB'C + A'BC$ ?                              | mplement the Boolean expression:          |

| a) 2                                                                                         | b) 3                                      |

| c) 4                                                         | d) 5                                   |

|--------------------------------------------------------------|----------------------------------------|

| (xxiii)                                                      |                                        |

| If the number of n selected input lines is equ select lines. | al to 2 <sup>m</sup> then it requires  |

| a) 2                                                         | b) m                                   |

| c) n                                                         | d) 2n                                  |

| (xxiv) The full form of ECL is                               |                                        |

| a) Emitter-collector logic                                   | b) Emitter-complementary logic         |

| c) Emitter-coupled logic                                     | d) Emitter-cored logic                 |

| (xxv) If A, B and C are the inputs of a full ac              | dder then the carry is given by        |

| a) A AND B OR (A OR B) AND C                                 | b) A OR B OR (A AND B) C               |

| c) (A AND B) OR (A AND B)C                                   | d) A XOR B XOR (A XOR B) AND C         |

| (xxvi) Half subtractor is used to perform sub                | traction of                            |

| a) 2 bits                                                    | b) 3 bits                              |

| c) 4 bits                                                    | d) 5 bits                              |

| (xxvii) The full subtractor can be implement                 | ed using                               |

| a) Two XOR and an OR gates                                   | b) Two half subtractors and an OR gate |

| c) Two multiplexers and an AND gate                          | d) Two comparators and an AND gate     |

| (xxviii) In an ECL the output is taken from _                | ·                                      |

| a) Emitter                                                   | b) Base                                |

| c) Collector                                                 | d) Junction of emitter and base        |

| (xxix) Which gates are ideal for checking the                | e parity bits?                         |

| a) AND                                             | b) NAND                                        |

|----------------------------------------------------|------------------------------------------------|

| c) EX-OR                                           | d) EX-NOR                                      |

| (xxx) When a high is applied to the Set l          | ine of an SR latch, then                       |

| a) Q output goes high                              | b) Q' output goes high                         |

| c) Q output goes low                               | d) Both Q and Q' go high                       |

| (xxxi) Which of the following is the Uni           | versal Flip-flop?                              |

| a) S-R flip-flop                                   | b) J-K flip-flop                               |

| c) Master slave flip-flop                          | d) D Flip-flop                                 |

| (xxxii) A NAND based S'-R' latch can b             | be converted into S-R latch by placing         |

| a) A D latch at each of its input                  | b) A D latch at each of its input              |

| c) It can never be converted                       | d) Both a D latch and an inverter at its input |

| (xxxiii) Ripple counters are also called _         |                                                |

| a) SSI counters                                    | b) Asynchronous counters                       |

| c) Synchronous counters                            | d) VLSI counters                               |

| (xxxiv) (A + B)(A' * B') = ?                       |                                                |

| a) 1                                               | b) 0                                           |

| c) AB                                              | d) AB'                                         |

| (xxxv) The excess-3 code for 597 is give           | en by                                          |

| a) 100011001010                                    | b) 100010100111                                |

| c) 10110010111                                     | d) 10110101101                                 |

| (xxxvi)                                            |                                                |

| On subtracting (001100) <sub>2</sub> from (101001) | 2 using 2's complement, we get                 |

| ·                                            |                                                |

|----------------------------------------------|------------------------------------------------|

| a) 1101100                                   | b) 011101                                      |

| c) 11010101                                  | d) 11010111                                    |

| (xxxvii)                                     |                                                |

| On subtracting (01010) <sub>2</sub> from (11 | 110) <sub>2</sub> using 1's complement, we get |

| a) 1001                                      | b) 11010                                       |

| c) 10101                                     | d) 10100                                       |

| (xxxviii) The expression for Abso            | orption law is given by                        |

| a) A + AB = A                                | b) $A + AB = B$                                |

| c) $AB + AA' = A$                            | d) A + B = B + A                               |

| (xxxix) A 3-variable Karnaugh r              | nap has                                        |

| a) 9 cells                                   | b) 8 cells                                     |

| c) 4 cells                                   | d) 16 cells                                    |

| (xl) In a multiplexer the output do          | epends on its                                  |

| a) Data inputs                               | b) Select inputs                               |

| c) Select outputs                            | d) None of these                               |

| (xli) When two 16-input multiple             | exers drive a 2-input MUX, what is the result? |

| a) 2-input MUX                               | b) 4-input MUX                                 |

| c) 16-input MUX                              | d) 32-input MUX                                |

| (xlii) The decimal equivalent of h           | nex number 1A53 is                             |

| a) 6793                                      | b) 6739                                        |

| c) 6973                                      | d) 6379                                        |

|                                              |                                                |

| b) DC1 d) 1DC l to a NOT gate serially, its b) 00110 d) 11001 A6 to 3A is b) E0 d) EF |

|---------------------------------------------------------------------------------------|

| d) 1DC I to a NOT gate serially, its b) 00110 d) 11001 A6 to 3A is b) E0              |

| b) 00110 d) 11001 A6 to 3A is b) E0                                                   |

| b) 00110 d) 11001 A6 to 3A is b) E0                                                   |

| d) 11001  A6 to 3A is  b) E0                                                          |

| A6 to 3A is b) E0                                                                     |

| b) E0                                                                                 |

| ,                                                                                     |

| d) EF                                                                                 |

|                                                                                       |

|                                                                                       |

| b) Combinational logic circuits                                                       |

| d) Several SSI logic gates or combinational logic circuits                            |

| bit serial adder?                                                                     |

| b) 3                                                                                  |

| d) 5                                                                                  |

|                                                                                       |

| b) It's fan-out capability is high                                                    |

| d) It is slow                                                                         |

| ,                                                                                     |

| erformed by which properties                                                          |

|                                                                                       |

|                                                                                       |

| (l) Which is an incorrect rule of binary subtract                                               | tion from the following?                                                                             |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| a) $0 - 0 = 0$                                                                                  | b) $0 - 1 = -1$                                                                                      |

| c) $1 - 0 = 1$                                                                                  | d) $0 - 1 = 1$ with borrow '1'                                                                       |

| (li)                                                                                            |                                                                                                      |

| Binary subtraction of 100101 – 011110 is                                                        |                                                                                                      |

| a) 000111                                                                                       | b) 10101                                                                                             |

| c) 111000                                                                                       | d) 101010                                                                                            |

| (lii) Perform multiplication of the binary numb                                                 | pers: $01001 \times 01011 = ?$                                                                       |

| a) 001100011                                                                                    | b) 110011100                                                                                         |

| c) 10100110                                                                                     | d) 101010111                                                                                         |

| (liii) There are many situations in logic design expression is possible in terms of XOR and     | -                                                                                                    |

| a) X-NOR                                                                                        | b) X-OR                                                                                              |

| c) NOR                                                                                          | d) NAND                                                                                              |

| (liv) If A and B are the inputs of a half adder, to                                             | he sum is given by                                                                                   |

| a) A AND B                                                                                      | b) A OR B                                                                                            |

| c) A XOR B                                                                                      | d) A EX-NOR B                                                                                        |

| (lv) When performing subtraction by addition is                                                 | n the 2's-complement system                                                                          |

| a) The minuend and the subtrahend are both changed to the 2's-complement                        | n b) The minuend is changed to 2's-<br>complement and the subtrahend is left in its<br>original form |

| c) The minuend is left in its original form and the subtrahend is changed to its 2's-complement | d) The minuend and subtrahend are both left in their original form                                   |

| (lvi) Standard TTL circuits operate with a v                                                    | olt power supply                                                                                     |

| a) 2                                                                           | b) 5                                                         |

|--------------------------------------------------------------------------------|--------------------------------------------------------------|

| c) 4                                                                           | d) 6                                                         |

| (lvii) In RTL NOR gate, the output is at logic 1                               | only when all the inputs are at                              |

| a) logic 0                                                                     | b) logic 1                                                   |

| c) +10V                                                                        | d) Floating                                                  |

| (lviii) The primary advantage of RTL technolog                                 | gy was that                                                  |

| a) It results as low power dissipation                                         | b) It uses a minimum number of resistors                     |

| c) It uses a minimum number of transistors                                     | d) It operates swiftly                                       |

| (lix) TTL circuits with "totem-pole" output stag                               | ge minimize                                                  |

| a) The power dissipation in RTL                                                | b) The time consumption in RTL                               |

| c) The speed of transferring rate in RTL                                       | d) Propagation delay in RTL                                  |

| (lx) The way to speed up DTL is to add an acro                                 | ss intermediate resister is                                  |

| a) Small "speed-up" capacitor                                                  | b) Small "speed-up" transistor                               |

| c) Large "speed-up" capacitor                                                  | d) Large "speed-up" transistor                               |

| (lxi) A digital multiplexer is a combinational ci                              | rcuit that selects                                           |

| a) One digital information from several sources and transmits the selected one | b) Many digital information and convert<br>them into one     |

| c) Many decimal inputs and transmits the selected information                  | d) Many decimal outputs and accepts the selected information |

| (lxii) The selector inputs to an arithmetic/logic                              | unit (ALU) determine the                                     |

| a) Selection of the IC                                                         | b) Arithmetic or logic function                              |

| c) Data word selection                                                         | d) Clock frequency to be used                                |

| (lxiii) The minimum and maximum number of input AND gate is                    | transistors can be used by 2                                 |

| a) 2 & 3                                                                                      | b) 3 & 2                    |

|-----------------------------------------------------------------------------------------------|-----------------------------|

| c) 4 & 5                                                                                      | d) 5 & 4                    |

| (lxiv) The basic R-S flip-flop is                                                             |                             |

| a) A monostable multivibrator                                                                 | b) A bistable multivibrator |

| c) An astable multivibrator                                                                   | d) A Schmitt trigger        |

| (lxv) Which of the following circuits com logic circuits? 1. Full adder 2. Full subtractions. |                             |

| a) 1 only                                                                                     | b) 3 and 4                  |

| c) 4 and 5                                                                                    | d) 1, 2 and 3               |

| (lxvi) If an active-HIGH S-R latch has a 0 and then the R input goes to 0, the latch w        | vill be                     |

| a) SET                                                                                        | b) RESET                    |

| c) Clear                                                                                      | d) Invalid                  |

| (lxvii) One example of the use of an S-R                                                      | flip-flop is as             |

| a) Transition pulse generator                                                                 | b) Racer                    |

| c) Switch debouncer                                                                           | d) Astable oscillator       |

| (lxviii) A 4-bit shift register that receives by position for each                            | •                           |

| a) Right, one                                                                                 | b) Right, two               |

| c) Left, one                                                                                  | d) Left, three              |

| (lxix) A ripple counter's speed is limited l                                                  | by the propagation delay of |

| a) Each flip-flop                                                                             | b) All flip-flops and gates |

| c) The flip-flops only with gates                                                             | d) Only circuit gates       |

|                                                                                               |                             |

(lxx) Which of the following circuit can be used as serial to parallel converter?

a) Multiplexer

b) Demultiplexer

c) Decoder

d) Digital counter