## **BRAINWARE UNIVERSITY**

Term End Examination 2023-2024 Programme - Dip.EE-2021 Course Name - Basic Electronics Course Code - DEE303 (Semester III)

Brainware University

Time: 2:30 Hours [The figure in the margin indicates full marks. Candidates are required to give their answers in their Full Marks: 60 own words as far as practicable.]

## Group-A

1 x 15=15

- (Multiple Choice Type Question) Choose the correct alternative from the following: (i) Choose the base current amplification factor  $\beta$  is given by b) IB/IC a) IC/IB d) IB/IE c) IE/IB (ii) Tell, the doping of the emitter region of a transistor is b) Less than that of collector region a) Larger than that of collector region d) None of these c) Equal to that of collector region (iii) Select the option for which semiconductor diode is used b) rectifier a) oscillator d) None of these c) amplifier (iv) Cite the acceptor impurities b) Generate holes a) Generate electrons d) All of these c) Generate hole and electrons (v) If FET employed in cut-off, the depletion layers are b) Close together a) Touching each other d) None of these c) Far apart (vi) A FET produce output due to b) Minority carriers a) Majority carriers only d) Positively charged ions c) Positive and negative ions (vii) Identify the option which represent p-n junction diode's dynamic conductance is directly proportional to

- a) The applied voltage

b) The temperature

c) Its current

- d) None of these

- (viii) During reverse bias, a small current develops which is named as

- a) Forward current

b) Reverse current

c) Reverse saturation current

- d) Active current

- (ix) Identify which of the following is true in construction of a transistor?

- a) The collector dissipates less power

- c) The collector is made physically larger than the emitter region

- (x) Identify the Universal Gate

- a) AND

- c) NAND (xi) Identify the terminal of JFET

- a) anode, cathode, grid source, gate, drain

carriers

b) emitter, base, collector d) none of them

b) alpha = beta / (beta + 1)

d) beta = 1/(1 - alpha)

- e) source, gate, drain

(xii) Choose out off voltage if the pinch off voltage of JFET is 5V.

b) 5 V

d) 0 V

b) OR

d) XOR

- c) 7.5 V (xiii) Relate between alpha and beta

- a) beta = 1+(alpha-1)

- c) alpha= beta /(beta 1)

- (xiv) Identify active region of a transistor

- a) Both emitter and collector junctions are reverse biased

- c) Emitter junction is forward biased and collector junction is reverse biased

- b) Both emitter and collector junctions are reverse biased

b) The emitter supplies minority carriers

d) The collector collects minority charge

- d) None of these

- (xv) For a p-n-p transistor in CE mode,  $\beta$ =100, then identify the value of  $\alpha$  of the transistor

- a) 0.99

- c) 9.9

- b) 0.099

- d) 99

## Group-B

(Short Answer Type Questions)

3 x 5=15

(3)

(3)

(3)

- 2. Explain feedback and why it is required.

- 3. Develop the gain of a system with negative feedback.

- 4. Explain different series feedback amplifier topologies.

- 5. Explain different shunt feedback amplifier topologies.

- (3) (3)

- (3)

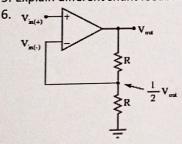

Write the transfer function (input/output equation) for an operational amplifier with an open-loop voltage gain of 100,000, and the inverting input connected to a voltage divider on its output terminal (so the inverting input receives exactly one-half the output voltage). In other words, develop an equation describing the output voltage of this op-amp (Vout) for any given input voltage at the non-inverting input (Vin():

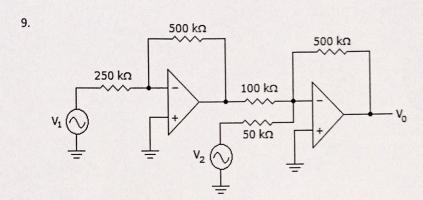

$$V_o = \frac{R_3}{R_1 + R_3} \frac{R_2 + R_4}{R_2} V_1 - \frac{R_4}{R_2} V_2$$

Propose how many op-amps are required to implement this equation?

## Group-C

(Long Answer Type Questions)

7. Explain the functionality of 3:8 decoder

- (5)

- 8. A JFET has I<sub>DSS</sub>= 12 mA and V<sub>GS(off)</sub>= -4V. Determine the minimum value of V<sub>DD</sub> required to (5) put the device in the constant current region of operation.

(5)

Evaluate the output voltage  $V_0$  if  $V_1 = -V_2 = 300$  mV.

10. Describe the various methods used for transistor biasing.

(5)

11. Explain base resistor method of transistor biasing.

(5)

12. Design an non - inverting amplifier and derive its gain.

(5)

OR

Design a subtractor circuit using op-amp.

(5)